# EMC設計への取り組み（II）

## Efforts toward EMC design (II)

平林 勝次 *Katsuji Hirabayashi*

花本 秀夫 *Hideo Hanamoto*

立田 次郎 *Jiro Tatsuta*

### 要旨

急激に高性能化、高集積化している自動車用の電子機器は、EMC性能の確保が年々困難になっている。このため、当社ではEMC設計品質向上活動を推進しており、前回は①当社を取り巻くEMC環境、②EMC設計の現状、③EMC設計織り込みの必要性、④要素技術の開発、⑤EMC設計の成功例について紹介した。EMC設計品質を更に向上していくには、上記に加えて全設計者のEMC設計スキル向上が不可欠である。また、将来を見越した要素技術開発推進やEDA環境の構築なども重要なとなる。今回（最終回）は、これら①EMC設計教育への取り組み、②将来に向けたEMC要素技術開発、③EDA環境の整備と活用、④デバイスに対するEMC設計について紹介する。

### Abstract

Automotive electronic devices, which have achieved high levels of performance and integration, now have the problem of requiring improved EMC performance year by year.

In response to this, Fujitsu Ten promotes improvement activities for EMC design quality, and in the previous article, we introduced the following five items:

① EMC regulations and requirements for Fujitsu Ten, ② Current situation of EMC design, ③ Necessity for EMC design incorporation, ④ Development of EMC elemental technology, ⑤ Successful examples of EMC design

For further improvement of EMC design quality, the development of EMC design skills by all designers is necessary in addition to five items mentioned above. As well, the promotion of elemental technology development or establishment of EDA tools with an eye to the future becomes important.

In this article (the last one), we introduce the following four items:

① Efforts for EMC design education, ② EMC elemental technology development for the future, ③ Development and utilization of EDA tools, ④ EMC design for devices

## 1

## はじめに

前回（第50号）は、①当社を取り巻くEMC環境、②EMC設計の現状、③EMC設計織り込みの必要性、④要素技術の開発、⑤EMC設計の成功例について紹介した。

今回は、①EMC設計教育への取り組み、②将来に向けたEMC要素技術開発、③EDA環境の整備と活用、④今後の取り組み、⑤EMC設計の成功例-2について説明する。

## 2

## EMC設計教育への取り組み

## 2.1 教育の必要性

前回は実践的な設計手法や要素技術開発、設計例を述べた。これらノウハウを各製品開発で適切に使用するには、各設計担当者のEMC設計スキル向上が不可欠である。

これには、EMC基礎から設計応用、対策方法まで体系立てた教育システムが必要であるが、十分には整備されていなかった。

例えば、従来のEMC設計の教育方法を振り返ると、各設計部門はベテラン設計者の経験則の伝承が主となっており、若手技術者の体系的な教育はほとんど行われていない。

この結果、若手設計者がEMC設計や対策を指示されたとき、理論的な内容の理解が不十分なまま闇雲に設計や対策検討に走ることもあった。

しかし、基本的なEMC設計理論を理解していれば、製品設計時や不具合対策時の方向性を見誤ることなく、効率的な設計や対策を進めることができる。

以上のように、EMC設計品質の向上にはEMC基礎から応用に至る体系立てた教育が必須である。

当社では実践に即したEMC設計講習会を開催し、若手設計者からベテラン設計者まで幅広くレベルアップを図っている。

## 2.2 EMC設計講習会

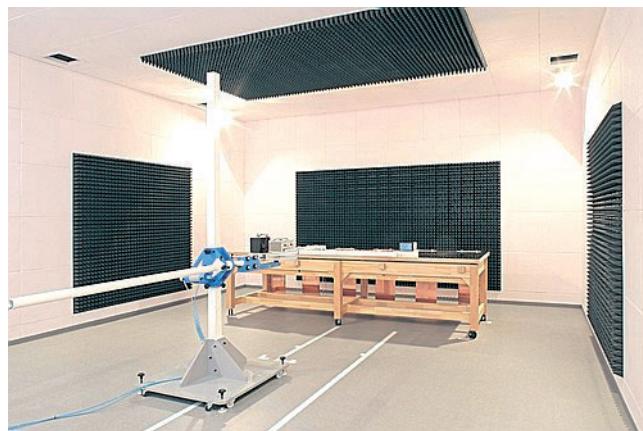

EMCの理論的な理解を深めるため、EMC設計講習会を開催している。講習会の一覧を表1に、講習会の様子を図1に示す。

表1 EMC設計講習会一覧表

Table 1 List of EMC Design Seminar

|   | EMC講習会一覧   | 対象者          | 講習内容                        |

|---|------------|--------------|-----------------------------|

| ① | 新人社員教育     | 技術系新入社員      | EMC基礎(EMC、EMC問題、EMC設計概論)    |

| ② | 基礎技術講習     | 基礎を知りたい方     | EMC基礎、ノイズ、電磁波、基礎計算、EMC設計概論  |

| ③ | 電気設計講習     | 電気設計技術者      | EMC構想、機構、回路、パターン、対策技術、対策事例等 |

| ④ | 機構設計講習     | 機構設計技術者      | EMC構想、機構、対策技術と対策事例等         |

| ⑤ | CADオペレータ講習 | 電気系のCADオペレータ | EMC基礎教育、回路基礎、パターン設計手法       |

| ⑥ | 出張講習       | 希望部門         | 基礎～設計、対策全般（希望内容に合わせる）       |

図1 EMC設計講習会の様子

Fig.1 Picture of EMC Design Seminar

ここでは、EMCとは何かという基本的な内容から教育を始め、EMC性能向上に効果的な高周波の基礎知識を教育する。

その後に回路設計者、基板設計者、機構設計者と分類して分野別に教育を進め、それぞれの設計担当者の理解を深めていく。

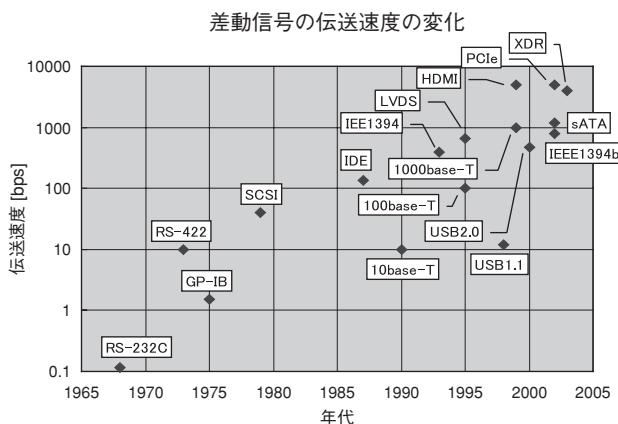

## 2.3 教育方針

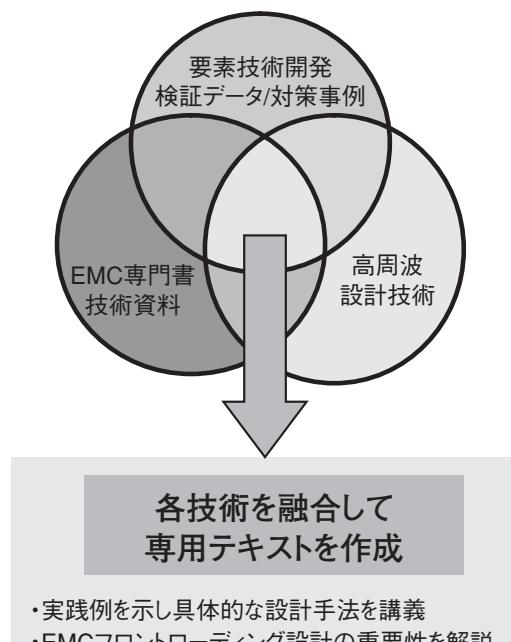

当社では講習会の内容充実に注力しており、教育方針を明確化した上で専用テキストを作成し、講習会で使用している。

講習会は、各講習会とも理論的な解説は行うが数式は必要最小限に留め、「①まずはイメージで理解する、②具体的にどう設計するか、③どのように応用・対策するか」という実践的な内容としている。

専用テキストは、設計手法を解説しながら具体的な数値をできる限り示し、設計指針としている。

例えば、基板設計では目的に適したガードパターン幅の推奨値を示している。また、機構設計では放熱の開口部について選定すべき形状や寸法などを示している（図2、3参照）。

図2 専用テキストの作成と活用

Fig.2 Creation and Utilization of Special Textbook

図3 専用テキスト抜粋

Fig.3 Extract from Special Textbook

以上の教育方針で受講者の実践的な理解を深め、製品開発に直結するような教育を行っている。

なお、理論的な理解をさらに深めたい設計者には個別に講習を行うほか、社外のセミナーへの参加を推奨し、さらなる技術力向上を支援している。

## 2.4 オーソリティ・エンジニア育成

教育の課題として、EMC設計のオーソリティ・エンジニア（以下 EMC-AE という）育成があげられる。

EMC-AE とは、EMC設計やEMC不具合対策の知見を持ち、EMC-DR（EMC-Design Review）などの場面で改善点や問題点を指摘できる技術者である。

この育成には候補者が、講習会や自己学習にて基本的な知識と一般的な応用技術を学び、EMC設計・対策にて実践を積む。さらに多くのEMC-DRに参加しながら幅広い知識を得ることが不可欠である。

現時点では EMC-AE の人員数は十分ではないが、将来的には各設計部門に EMC-AE が配置できるよう検討していく。

この配置が進めば、全社的に効率的な EMC 設計の織り込みが可能になり、さらなる EMC 設計品質向上が期待できる。

## 3 将来に向けたEMC要素技術開発

### 3.1 将来的なEMC要素技術開発

教育の重要性について述べてきたが、自動車用電子機器は、今後さらに高度化、複雑化するため、教育内容も同様にレベルアップしなければならない。

このためには EMC 設計で使用するための要素技術の継続的な開発が不可欠である。

開発の範囲は筐体から基板、回路、部品まで多岐に渡っているが、要素技術開発の例として高速伝送線路の開発について以下に述べる。

### 3.2 ケーブルによる高速伝送線路の開発

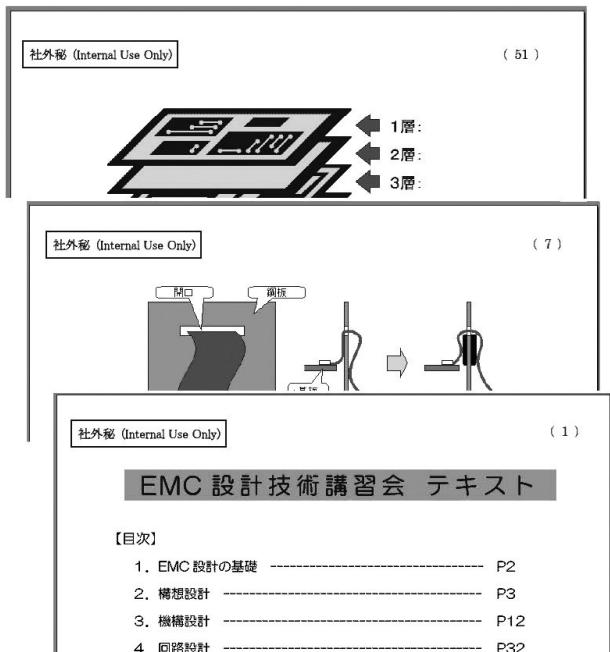

テレビ画面のハイビジョン化に伴い画像データ伝送方式が変化し始めている。

高速にデータを伝送する差動伝送方式の一つである LVDS 方式<sup>注(1)</sup> が自動車用電子機器の分野でも採用が始まりつつある。

差動伝送方式の動向を図4に示す。

注(1) LVDS 方式：伝送速度 数100Mbps以上が可能な差動伝送方式。今後、車載用電子機器の画像データ伝送で主流になると予想される。

図4 差動伝送方式の伝送速度

Fig.4 Transmission Rate of Differential Transmission System

高速データ通信媒体の検討例を示す。

従来より、自動車用電子機器はFPC（フレキケーブル）にて本体とディスプレイ部を接続する場合が多い。しかし、データ伝送の高速化に伴い、FPCでは波形の乱れなど伝送品質の劣化や、ケーブルからのエミッションノイズ発生などのEMC問題が想定される。

細線同軸ケーブルの採用が一つの対策案だが、大幅なコストアップが懸念される。このため、FPCと細線同軸ケーブルの比較検討を行った。

差動信号線路のEMC評価方法の一つに特性インピーダンスがある。

細線同軸ケーブルでは安定した特性インピーダンスが期待できるが、同軸構造を持たないFPCでは不安定な特性が予想され、比較検討の対象項目とした。

ここでは伝送線路の特性インピーダンスTDR<sup>注(2)</sup>の検討結果を紹介する。

TDR特性の乱れは反射によるエミッションノイズを増加させるため、最低限に抑える必要がある。

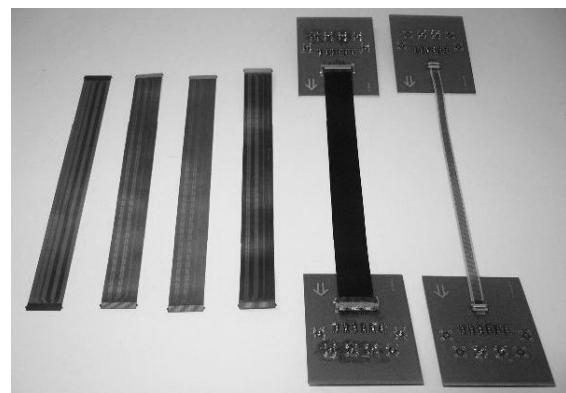

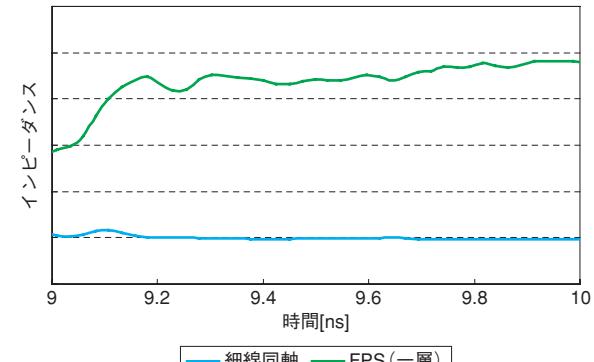

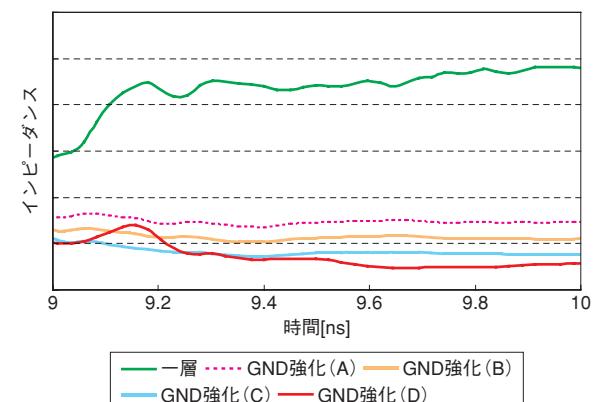

今回検討した細線同軸とFPCの試作品を図5に示し、TDRによる特性インピーダンス測定結果を図6と図7に示す。

通常のFPC（一層基板）では信号線路の特性インピーダンスが大きく乱れているのに対して、細線同軸ケーブルでは安定しており、性能面でもEMC面でも優位なことが読み取れる（図6）。

しかし、FPCであってもEMC設計を織り込み、GND強化することで細線同軸ケーブルに近い特性インピーダンスが得られることを確認できた（図7）。

図5 FPC（5種）と細線同軸試作品と検討用基板

Fig.5 FPC (5 types), Narrow Line Coaxial Prototype, and Printed Board for Evaluation

図6 細線同軸と通常のFPCの特性インピーダンス

Fig.6 Characteristics Impedance of Narrow Line Coaxial and Normal FPC

図7 FPC（5種）の特性インピーダンス

Fig.7 Characteristics Impedance of FPC (5 types)

注(2) TDR: TDR (Time Domain Reflectometry): 高速パルス信号を測定対象の伝送線路に加え、反射波を高速サンプリングオシロスコープで測定、演算することによりの伝送線路の特性インピーダンスを測定する方法。このインピーダンスは以下の式で求められる。反射の係数を $\rho$ とすると、

$$\rho = \frac{\text{反射電圧}}{\text{入射電圧}} = \frac{Z_L - Z_0}{Z_L + Z_0}$$

・ $Z_L$ ：求めたい伝送線路のインピーダンス

・ $Z_0$ ：TDR測定器のインピーダンス

$$Z_L = Z_0 \frac{1 + \rho}{1 - \rho}$$

このように、EMCとコストの両立を目指した設計技術を検証し、順次設計部門に展開している。

### 3.3 SI設計とEMC設計

前項は高速伝送線路で使用するケーブルについて述べたが、基板内のデバイス間も高速な伝送線路で接続される場合があり、EMC問題を発生している。

特に最近では、地上波デジタル放送のデコード基板などにはパソコンと同様の高速メモリを搭載しており、従来車載機器では必要でなかった「SI設計（Signal Integrity）」が必須となっている。

SI設計とは、高速伝送線路における線路長やインピーダンスを適切に設計して反射を抑え、なまりや遅延、リンクのない波形が得られるよう配線設計を適切に行うことである。

しかし、SI設計はEMC設計と両立しない面があり注意が必要である。

具体的には、高速伝送線路でデジタル通信を行った場合、エミッションノイズが発生しやすい。このため、ダンピング抵抗などを信号ラインに挿入して対策する場合があるが、なまりや遅延が発生して波形品質を損なう恐れがある。

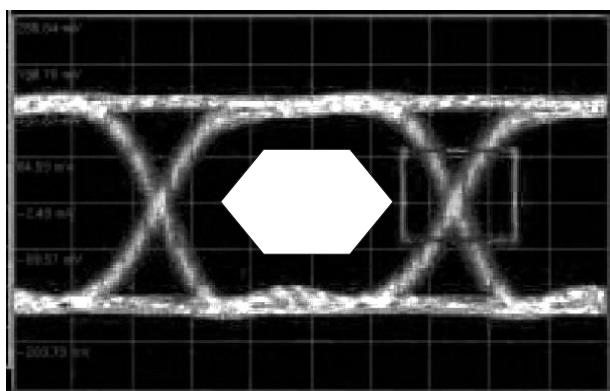

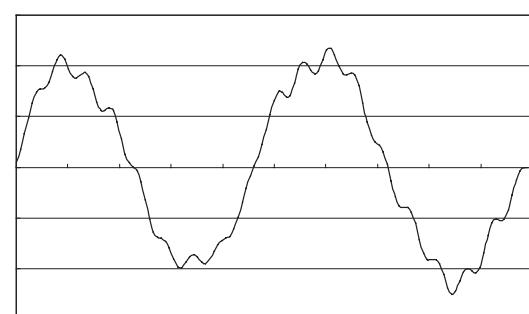

波形品質の確認例を図8に示す。SIの確保には中央のひし形部が開口するよう設計する必要があるが、エミッションノイズを低減するため信号ラインへダンピング抵抗を挿入すると開口部分が閉じてしまうことがある。

以上のように、SI設計とEMC設計はトレードオフの関係を持ち、バランスの良い設計が要求される。

信号のアイパターンを測定している状態

- ・中央のひし形が規格を示し、信号がひし形内に入るとNGになる。(開口率の低下)

- ・EMC(エミッション)対策すると開口率が低下し、波形品質が劣化する。

図8 高速伝送路の波形品質

Fig.8 Waveform Quality of High-Speed Transmission Line

### 3.4 要素技術開発の今後

高速伝送ケーブルの技術開発やSI設計との両立を紹介したが、EMC要素技術の開発課題は筐体から基板、回路、部品まで多岐に渡っている。

世の中の動向を鑑みると、パソコンや情報家電、最新ゲーム機で採用されている最新技術が自動車用電子機器に応用されてきており、パソコンや情報家電などの技術課題にも注目していく。

また、実機による要素技術検証を重視しているが、理論的な裏付けのため、電磁界シミュレーションも取り入れながらの検証が必要となる。

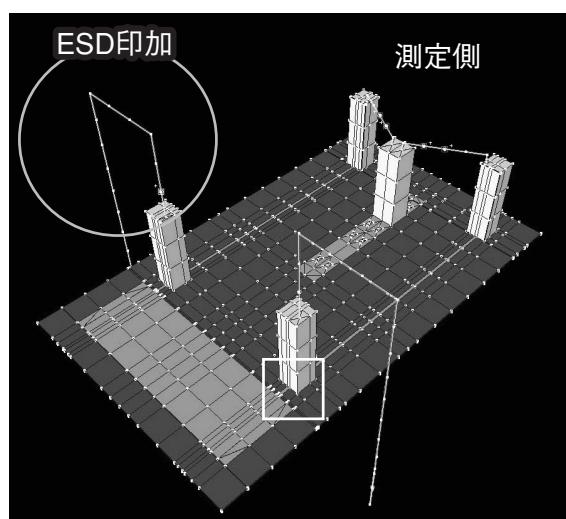

例として、ESD (Electro Static Discharge: 静電気放電)印加時の電磁界シミュレーション検証を紹介する。

図9はある点にESDを印加したときの測定点での電圧変化をシミュレーションするモデルである。

この例では、ESD印加による電圧変化を読み取り、実機の検証結果と比較しながら、対策部品の選定や基板パターンの修正などに利用することを目的としている。

図10にシミュレーションでの電圧変動の結果を示す。

図9 ESD検証用電磁界シミュレーションモデル

Fig.9 Electromagnetic Field Simulation Model for ESD Verification

図10 シミュレーションでの電圧変動結果例

Fig.10 Result Example of Voltage Fluctuation in Simulation

このように、実験による検証と並行して電磁界シミュレーションの検証を進めており、今後はさらに理論と実際の双方で確認しながら要素技術開発を進めていく。

## 4

## EDA環境の整備と活用

## 4.1 EDAの導入

EMC設計品質向上活動を進めていくには、EDA “Electronic Design Automation” 環境の整備が効果的である。EDAとは電気回路や基板などの設計を自動的に行うツールである。

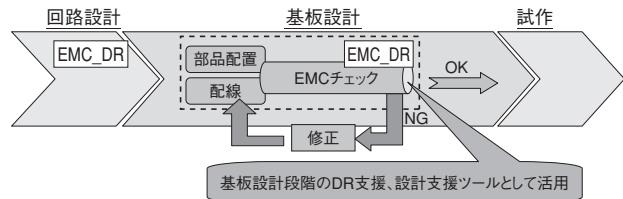

当社では、このEDA環境としてEMCルールチェッカを導入した。

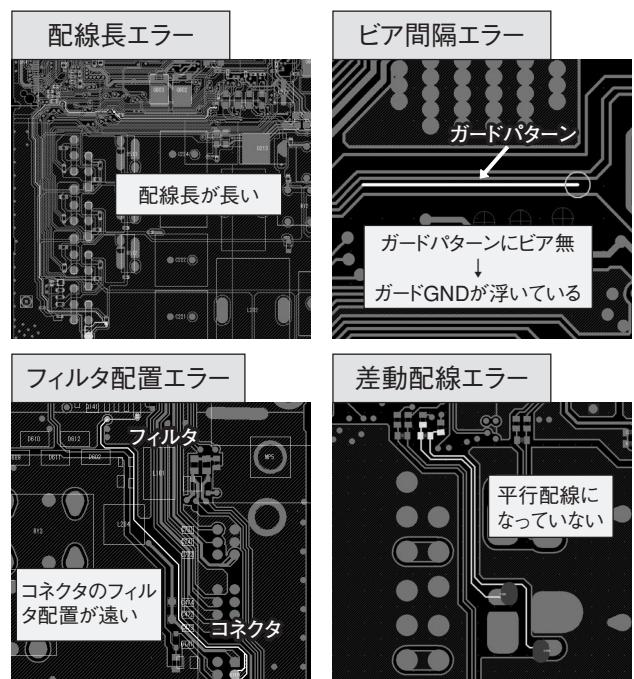

EMCルールチェッカとは、基板パターンの設計場面で使用するツールで、高集積・高密度化した目視での確認が困難な多層基板のパターンチェックを可能とするツールである。

## 4.2 EMCルールチェッカの利用

導入したEMCルールチェッカは、回路と基板の情報を入力し、解析を行うことでパターンの引き回しや部品の接続などのEMC的な改善点を表示する。

チェックの機能一覧を表2を示す。

表2 EMCルールチェッカ機能一覧

Table 2 List of EMC Rule Checker Functions

| ルール            | ルール概要              |

|----------------|--------------------|

| ① 配線長          | 信号配線の長さ            |

| ② VIA数         | 信号配線の層間接続数         |

| ③ 基板端          | ベタGND内側での信号配線      |

| ④ GVプレーンまたぎ    | 信号配線の層間接続直近でのキャパシタ |

| ⑤ リターンパス不連続    | 信号配線のリターンパス不連続     |

| ⑥ SGパターン有無     | 信号配線へのガードパターン      |

| ⑦ 放射電界         | 信号配線の放射電界強度        |

| ⑧ SGパターンVIA間隔  | ガードパターンへのVIA設定     |

| ⑨ プレーン外周       | ベタGNDへのVIA位置、VIA数  |

| ⑩ フィルタ         | コネクタ信号線のフィルタ配置と位置  |

| ⑪ デカップリングキャパシタ | LSI電源-GND間のキャパシタ有無 |

| ⑫ 差動信号         | 差動配線の配線長差、平行性      |

| ⑬ クロストーク       | 配線間のクリアランスと平行配線長   |

EMCルールチェッカは、チェック漏れを防止するためのツールとして使えば大きな効果が期待できる。

ただし、構想設計に関わるような基板全体に対して修正を指摘することはできないため、まずは構想設計をしっかり行うことが前提である。

また、各ルールには良否を判断するための閾値の設定が必要であり、この値の設定がノウハウとなる。

この閾値の検討では、当社の持つノウハウをルール化してチェックに組み込むことも考慮し開発を進めている。

EMCルールチェッカの量産設計適用プロセスを図11に、チェック結果の例を図12に示す。

図11 EMCルールチェッカ使用プロセス

Fig.11 Usage Process of EMC Rule Checker

図12 EMCルールチェッカ実行例

Fig.12 Implementation Example of EMC Rule Checker

## 5

## デバイスに対するEMC設計

EMC設計への取り組みについて述べてきたが、その他にも課題がある。

デバイスのEMC性能は製品全体でのEMC性能への影響が大きく、今後のデバイスの高機能化や高速化には十分な注意が必要である。

## 5.1 デバイスのEMC性能

電子デバイス単体のEMC性能が悪ければ、回路や基板、構造で良い設計を行っても、製品としてEMC性能が得ら

れない場合が多い。

このため、デバイスメーカーでは単体での評価法を検討しており、デバイス業界ではいくつかの方式が提案されている。

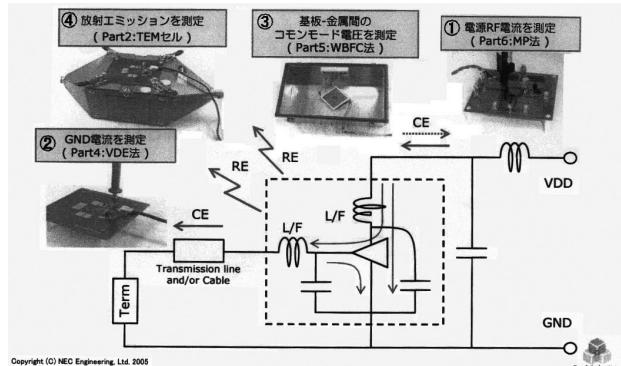

これら電子デバイス単体のEMC評価法を図13に示す。

|         |                           |

|---------|---------------------------|

| ①MP法    | デバイスの電源端子に流れるノイズ電流を測定     |

| ②VDE法   | デバイスのGND端子に流れるノイズ電流を測定    |

| ③WBFC法  | 基板-金属(筐体)間のノイズ電圧を測定       |

| ④TEMセル法 | セル内のテスト基板を配置して放射エミッションを測定 |

図13 電子デバイスのEMC評価法

Fig.13 EMC Evaluation Method of Electronic Device

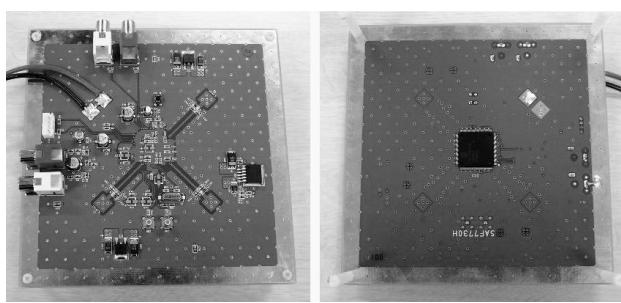

当社では、ノイズが多いとされているデバイスを選定して、テスト的にMP (Magnetic Probe Method: 磁界プローブ測定) 法の評価基板を製作した。

この評価基板を図14に示す。

基板表面

基板裏面

図14 MP法評価用基板

Fig.14 Printed Board for MP Method Evaluation

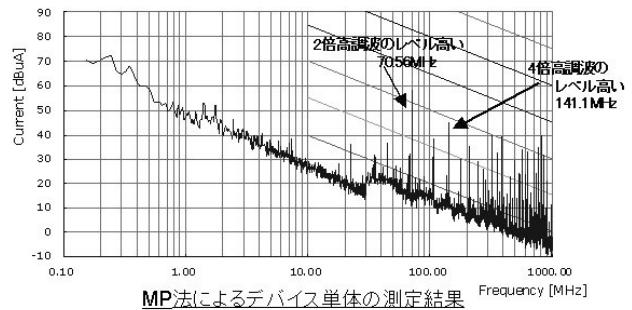

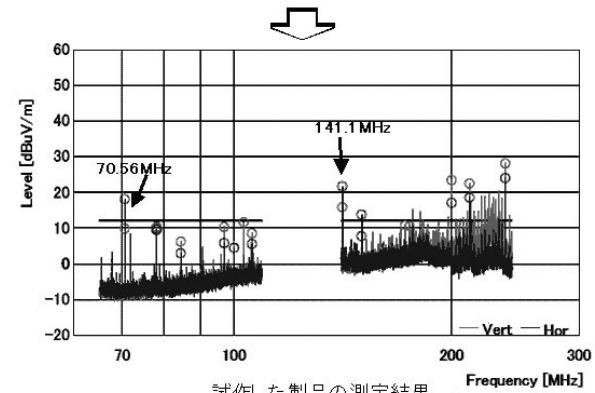

このMP法評価基板でデバイスのノイズを測定した結果と、試作した製品に同じデバイスを搭載した場合のEMC評価結果を図15に示す。

MP法によるデバイス単体の測定結果

試作した製品の測定結果

図15 デバイス単体と製品状態での比較

Fig.15 Comparison between Single Device and Finished Product

結果は、デバイス単体でノイズが発生している周波数は試作した製品でも同様のエミッションノイズが発生していることを確認できた。

さらにデバイス単体と製品に組み込んだときのノイズレベルは相関が取れていないことも確認した。

今後は相関を把握するために評価するデバイス数を増やしてデータの蓄積を進め、デバイスに必要なEMC性能を検討していく。

またMP法に限定せず各メーカーが採用している複数の測定法でも単体データを入手・蓄積し、デバイス単体と製品全体のエミッションノイズの相関を把握していく。

## 6

## 終わりに

当社のEMC設計への取り組みについて二回に分けて述べてきた。

EMC (ノイズ) は目に見えず動きが分かりにくいため、効率的な設計や不具合対策が行いにくい。

しかし、EMC設計のための適切な知識があれば、製品設計の構想段階からEMC設計技術を織り込むことができ、EMC性能が得られた効率的な製品設計を進めることができる。

これらを実現するため、今後も新技術に対応したEMC要素技術開発や、講習会などによる教育活動を継続すると

ともに、EDAツール環境の整備やデバイスEMC性能向上など、全社的な取り組みをさらに進め、EMC技術力向上を図っていきたい。

#### 参考文献

- ・株式会社 NEC情報システムズ：ホームページ「EMI抑制設計支援ツール DEMITASNX」資料

- ・小林 勝治（NEC エンジニアリング）：セミナー名「磁界プローブ（MP 法）によるノイズ計測システムのご紹介」、メーカ名「NEC エンジニアリング株式会社」（セミナー資料）

以上

記載した製品名などの固有名詞は、各社の商標または登録商標です。

#### 筆者紹介

平林 勝次

(ひらばやし かつじ)

1986年入社。以来、自動車用無線機器の開発を経て、EMC要素技術の開発とEMC設計教育に従事。現在、開発本部 EMC技術部に在籍。

花本 秀夫

(はなもと ひでお)

1978年富士通テン(株)入社。以来、自動車用電子機器の開発、品質管理、試作を経て、事業企画業務に従事。現在、開発本部EMC技術部長兼 中津川テクノセンター長。

立田 次郎

(たつた じろう)

1977年入社。以来、移動通信システムの開発に従事。技術支援関連業務を経て、現在、開発本部 EMC技術部チームリーダ。